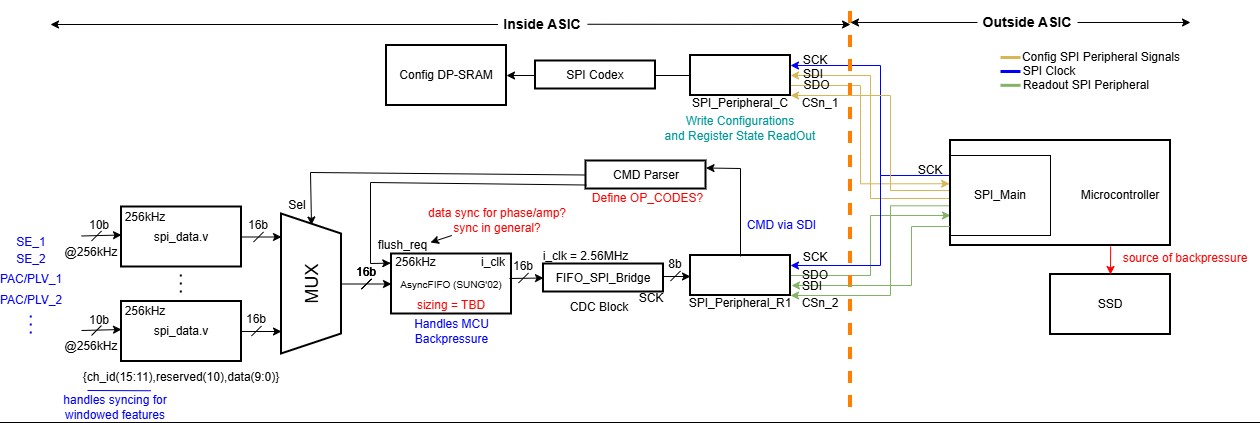

A streaming configuration schema for ASIC interfacing with Microcontrollers

Today, I have to work on implementing a sleek SPI subordinate module for one of our ASICs. While neural interfaces asics work great when testing in the lab with high-speed FPGAs for programming and configurability for high-bandwidth data recording but real-life ASICs need a more adaptable interface such as SPI which may not have the required data bandwidth to record all at once but SPI is fast enough to provide multiple parameters of interest. I am aiming to test this interface on the ARM microcontroller from ST Microelectronics talking to the RTL of SPI-S implemented on the FPGA.

Main challenge points would be figuring out the delays betweenCC and SCLK lines due to delays in the MCU processing (as the final MCU may be different from the one I am using to test) and I want to push the clock rate to as high as 20.48MHz. At that rate I can safely log data on the MCU end.